|

1 |

傾僫儘僌怣崋専弌儐僯僢僩 |

|

|

|

|

傾僫儘僌怣崋傪撉傒偲傞偵偼儃儕儏乕儉傗岝揹曄姺丄儅僀僋丄摫揹僑儉丄摍悢懡偔偺傕偺偑僙儞僒乕偲偟偰巊梡偱偒傑偡丅偦偺條側僙儞僒乕偵敪惗偟偨揹婥怣崋偺拞偵偼戝偒偝偺惉暘偺懠偵懍偝偺惉暘偑娷傑傟偰偍傝丄偙傟傜傪擟堄偵拪弌偱偒傟偽僀儞僞乕僼僃乕僗偲偟偰桳岠偵妶梡偱偒傑偡丅

偙偺儐僯僢僩偼愝掕儃儕儏乕儉偵傛傝怣崋偺儗儀儖丄怣崋偺懍搙偵懳偡傞姶搙傪愝掕弌棃傑偡丅

恾侾乣俁偵帵偡寁應攇宍偼媅帡揑偵僼傽儞僋僔儑儞僕僃僱儗乕僞偐傜俙俵曄挷傗僗僀乕僾怣崋偱擖椡偟偨応崌偵懳偡傞専弌弌椡傪婰榐偟偨傕偺偱偡丅恾侾丄偼摿掕偺墳摎廃攇悢偵墬偗傞怣崋儗儀儖偵懳偟偰偺墳摎摿惈偱偡丄枖丄恾俀丄恾俁丄偼偦傟偧傟墳摎廃攇悢偺愝掕傪儃儕儏乕儉偱壜曄偟偨応崌偺墳摎埵抲偑曄壔偟偰偄偔忬嫷傪昞偟傑偡丅

偙偺婡擻傪僗僀僢僠摦嶌偲偟偰墳梡偡傞応崌丄堦斒揑側儊僇僗僀僢僠偵斾妑偟偰嵟傕摿挜揑側偺偼憡懳揑側敾抐偑弌棃傞揰偱偡丅廬偭偰椺偊偽摫揹僑儉偺條側抏椡偺偁傞嵽椏傪僗僀僢僠偲偟偰庤偱帩偭偰憖嶌偡傞帪丄庤偵埇偭偨偩偗偱偼摦嶌偣偢乽偁傞掱搙偺懍搙乿丄乽偁傞掱搙偺嫮偝乿偺忦審偑廳側偭偨帪偩偗乽倧値乿偲敾抐偝偣傞帠偑弌棃傑偡丅

|

|

|

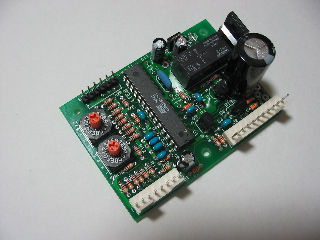

嵍偺幨恀偑晹昳傪僼儖幚憰偟偨儃乕僪偱偡丅

巊梡偟偰偄傞晹昳偼慡偰儕乕僪晹昳偱偡丅懡梡搑偺巊偄曽傪憐掕偟偰偄傞偺偱偁偊偰儕乕僪晹昳偵偟偰偁傝傑偡丅

夞楬恾傪尒偰偄偨偩偗傟偽偍傢偐傝偺條偵弌椡偑奺庬椶偐偺曽幃偱弌偣傞傛偆偵側偭偰偍傝丄幚嵺偼栚揑偵崌傢偣偨弌椡乮揹棳僽乕僗僩丄儕儗乕丄僆乕僾儞僐儗僋僞乯摍傪梡搑偵崌傢偣偰巊梡偟丄昁梫偺柍偄晹昳偼庢傝奜偟偰奺梡搑偵懳墳偟偰偄傑偡丅

俠俹倀偼俙俿俵俤俴幮偺俙俿倣倕倗倎俉傪巊梡偟偰傑偡丅偙偺俠俹倀偼奐敪僣乕儖偑柍彏偱岞奐偝傟偰偍傝丄僾儘僌儔儅乕傕娙扨偵嶌傟傑偡丅嶌傞偺偑柺搢側応崌偼捠斕偱係愮墌傎偳偱峸擖偱偒傑偡丅摉俫俹偺夞楬丄僐僣丄偺儁乕僕偱徯夘偡傞俀俁俀俠偺俬俠偲慻傒崌傢偣傟偽庤寉偵僨乕僞儘僈乕傗僙儞僒乕偺専弌憰抲偑嶌傟傑偡丅

僨乕僞儘僈乕偵墳梡偡傞応崌偺曽朄偼偙偪傜偺儁乕僕傪偛棗壓偝偄丅

|

|

|

偙偺儃乕僪傪偛擖傝梡偺曽偼偛楢棈傪偄偨偩偗傟偽懳墳偝偣偰偄偨偩偒傑偡丅

彯丄惂屼撪梕乮僜僼僩乯偵晅偄偰偺偍栤偄崌傢偣傪懡偔偄偨偩偒傑偟偨偑丄奺儐乕僓乕條偺

偛棙梡栚揑偵崌傢偣傞堊偵偼偦偺杦偳偺応崌儐乕僓乕條庒偟偔偼暰幮偺偄偢傟偐偵墬偄偰嶌傝捈偡帠偵側傝傑偡丄帺嶌偺応崌偼慜婜偟偨條偵奐敪娐嫬偑娙扨偵偦傠偊傜傟傑偡丅

偛嶲峫傑偱偵暰幮偱峴偆応崌偼偍傛偦偺栚埨偲偟偰椺偊偽撪梕偑忋婰偱偛徯夘偺傕偺偵嬤偄斖埻偱偁傟偽僇僗僞儅僀僘偺旓梡偲偟偰栺侾侽枩墌慜屻偲側傝傑偡丅

|

|

2 |

懡們倛惗懱怣崋僥儗儊乕僞 |

|

|

|

|

忋偺幨恀偼怱揹恾傗嬝揹恾偦偺懠偺惗懱怣崋傪専弌偟丄揹攇偱憲怣偡傞婎斅偱偡丅

偙偺條側憰抲偺応崌堦斒揑偵偼彫揹椡柍慄偺揹攇傪巊梡偟扨嶰丄扨巐側偳偺姡揹抮偵傛傝嬱摦偝傟傑偡偑丄摉憰抲偱偼彫宆壔偺堊偵儃僞儞揹抮傪巊梡偟丄嬌傔偰旝彮側揹椡偱憰抲慡懱傪嬱摦偡傞昁梫偑偁傞偙偲偐傜旝庛揹攇傪巊梡偟偰偄傑偡丅

憰抲偼俈們倛偺惗懱傾儞僾丄俙乛俢丄俥俹俧俙丄柍慄夞楬偱峔惉偝傟丄偙傟傜偺揹椡傪俁倁偺儃僞儞揹抮偵傛傝丄憤崌揹棳栺係侽侽儅僀僋儘傾儞儁傾偱丄杽傔崬傑傟偨摦暔偺懱撪偐傜栺俁儢寧偺娫拫栭楢懕偟偰寁應怣崋傪弌偟懕偗傞帠偑弌棃傑偡丅

|

|

3

|

挻崅懍俥俹俧俙丒挻掅徚旓揹椡俠俹俴俢丂

|

|

|

僓僀儕儞僋僗偺俥俹俧俙丄倁倝倰倲倕倶係僔儕乕僘傪巊梡偟偨俥俹俧俙儃乕僪乮嵍懁乯丄暲傃偵挻掅徚旓揹椡俠俹俴俢傪巊梡偟偨儃乕僪乮塃懁乯偱偡丅

乽崅懍俥俹俧俙乿

俽倫倎倰倲倎値丄倁倝倰倲倕倶摍偺僔儕乕僘偵偼乽俢俴俴乿偑撪憼偝傟偰偍傝丄僋儘僢僋擖椡抂巕偐傜擖椡偟偨怣崋傪帺桼偵掽攞偟偨傝暘廃偟偨傝弌棃傑偡丅偙傟傜偼偦傟偧傟帺桼偵惍悢偱巜掕弌棃傞偺偱椺偊偽侾侽侽俵俫倸偺僋儘僢僋傪擖椡偟偰俇掽攞偟偨傕偺傪俆暘廃偡傞偲侾俀侽俵俫倸偺僋儘僢僋偑惗惉弌棃傑偡丅偟偐偟丄嵟嬤偺僋儘僢僋敪怳婍偼杦偳偑俹俴俴側偺偱僋儕僗僞儖傪拲暥偟偰偄偨帪偺條偵擺婜偲偺寭偹崌偄偱嬯偟傓帠傕柍偔側傝丄偙偺婡擻偺昁梫惈偼偁傑傝姶偠傜傟傑偣傫偑丄巊梡廃攇悢偑崅偔側傞偲彮偟條巕偑曄傢傝傑偡丅

侾侽侽俵俫倸傪挻偊偨僋儘僢僋偑昁梫側応崌丄敪怳婍偺昳庬偑彮側偔側傝壙奿傕忋偑傝傑偡丅枖丄俥俹俧俙傑偱偺怣崋揱憲傕拲堄偑昁梫偲側傞堊偦傟偩偗偱傕愝寁忋偺儕僗僋偑崅偔側偭偰偟傑偄傑偡丅偙偺帪俢俴俴傪巊梡偡傞偲堦扷僋儘僢僋擖椡抂巕傑偱偼擟堄偺掅偄廃攇悢偱愙懕偟偰偦偺屻撪晹偱掽攞傪偡傟偽敪怳婍偺壙奿傗怣崋偺庢埖偵擸傓昁梫傕柍偔側傝傑偡丅枖丄俢俴俴偐傜偼俋侽搙丄侾俉侽搙丄俀俈侽搙偺埵憡僔僼僩偝傟偨怣崋偑僌儘乕僶儖儔僀儞偱巊梡偱偒傞偺偱埨掕偟偨崅懍張棟偑婥妝偵峴偊傑偡丅

偙傟傜偺怣崋傪崅廃攇偺僗儁傾僫偱娤應偡傞偲梊憐埲忋偵埨掕側僗儁僋僩儖傪偟偰偄傑偡丅嫭懷堟偺傾僫儘僌揱憲梡搑偵巊梡偱偒傞掱偺俠俶偱偼偁傝傑偣傫偑僶乕僗僩忬偵僉儍儕傾傪憲怣偡傞僔僗僥儉偵偼偦偺傑傑巊偊偦偆偱偡丅怣崋儗儀儖傕廫暘偁傞偺偱娙扨側揹椡憹暆傪峴偊偽偦偺傑傑揹攇偲偟偰旘傫偱峴偒傑偡丅庴怣偵俵倝們倰倕倢偺俬俠側偳傪巊梡偡傟偽偁傑傝柍慄偺抦幆偑柍偔偰傕僉乕儗僗僄儞僩儕乕傗惂屼憰抲偑嶌傟傑偡丅

偦傫側帠傪偟側偑傜忋婰幨恀偱偼俁侽侽俵俫倸晅嬤傑偱掽攞偟偰撪晹張棟媦傃奜晹僨僶僀僗偲偺愙懕傪峴偭偰偄傑偡丅幨恀偱偼巆擮側偑傜尒偊傑偣傫偑丄婎斅偼俆侽兌偺僀儞僺乕僟儞僗偲側傞傛偆偵愝寁偝傟偰偍傝丄撪憌偵墬偄偰慄楬挿傗摿惈僀儞僺乕僟儞僗傪挷惍偟丄俴倁俢俽傗俽俽俿俴摍偺擖弌椡抂巕傪帩偮廃曈偺崅懍僨僶僀僗偵愙懕偟偰偄傑偡丅

乽挻掅徚旓揹椡偺俠俹俴俢乿

塃偺幨恀偺俠俹俴俢偼傾僫儘僌張棟偺俙乛俢偺惂屼傗僨乕僞僗僩儕乕儉惗惉偺堊偵俽俼俙俵偺僶僢僼傽傪巊梡偟側偑傜傕俠俹俴俢偱偺徚旓揹棳偑侾丏俉倁摦嶌偱栺侾侽侽儅僀僋儘傾儞儁傾丄廃曈儘僕僢僋傪崌傢偣傞偲栺俀侽侽儅僀僋儘傾儞儁傾埲壓偺揹棳偱慡偰偺摦嶌傪峴偭偰偄傑偡丅

俠俹俴俢偱偼僋儕僗僞儖偺敪怳偑弌棃側偄偺偱奜晹偵愝偗偨俠俵俷俽僨僶僀僗偱帪寁梡偺僋儕僗僞儖傪敪怳偝偣偰偄傑偡偑慡偰偺夞楬偑嬌傔偰崅僀儞僺乕僟儞僗偲側傞堊儘僕僢僋夞楬傪庢傝埖偭偰偄傞姶妎偑側偔側偭偰偟傑偄傑偡丅

|

|

4 |

偦偺懠丂 |

|

|

|

|

偦偺懠丄傾僫儘僌偲僨傿僕僞儖傪愙懕偡傞媄弍傪拞怱偲偟偰奺暘栰偱偺奐敪傪峴偭偰偍傝傑偡丅

掅徚旓揹椡偺倧倫亅俙倣倫傪巊梡偟偨惗懱旝庛怣崋張棟夞楬傗嬤愒奜慄傪巊梡偟偨俽倫倧俀丄俬倰俢俙摍偺岝寁應怣崋張棟丄偦偟偰偦傟傜偺怣崋傪俠俹倀丄俠俹俴俢傪巊梡偟偰儀乕僗僶儞僪張棟傪峴偄柍慄憲怣婡丄庴怣婡偱僨乕僞揮憲傪峴偄俹俠偵僨乕僞傪搉偡張棟傑偱堦娧偟偰峴偭偰偍傝傑偡丅

|

|